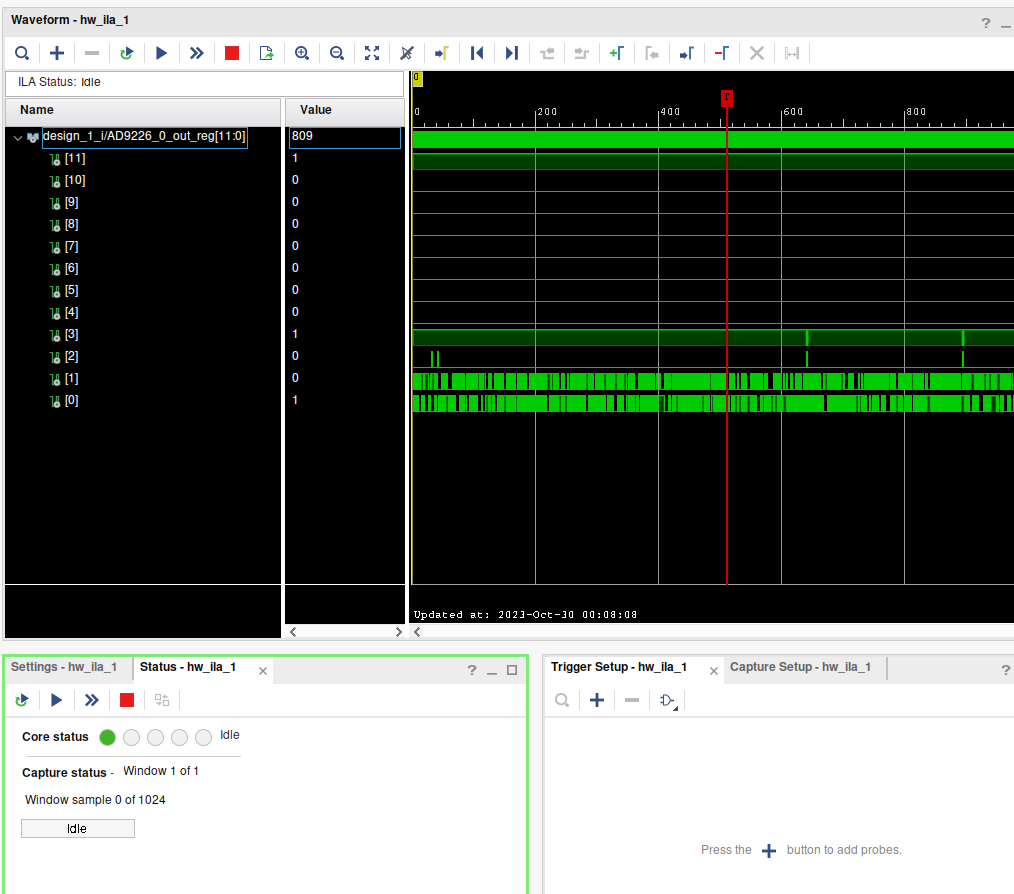

This is mostly a note for myself, but maybe it will eb useful. I struggled for too long to get the ILA logic analyzer up and running in Vivado for a simple project. It seemed I was missing a lot of knowledge. Here's a step-by-step in getting it running on an FPGA in Vivado 2023.1 with a simple vhdl model:

Create a new project, Make it an RTL project. Create a new source, AD9226.vhdl. Set the target language to VHDL. Create a new constraints file. Reference the EBAZ4205 dev board.

Replace the contents of the ad9226.vhdl file with:

Replace the constraints file with: (Note that you'll need to modify this for your pinouts), Discussion following:

For the constraints file, I have the pins set as normal, but I also had to tell the system the IO voltage of the output register, I had to mark it as debug so it wouldn't be optimized away. Probably not needed is the pulldowns.

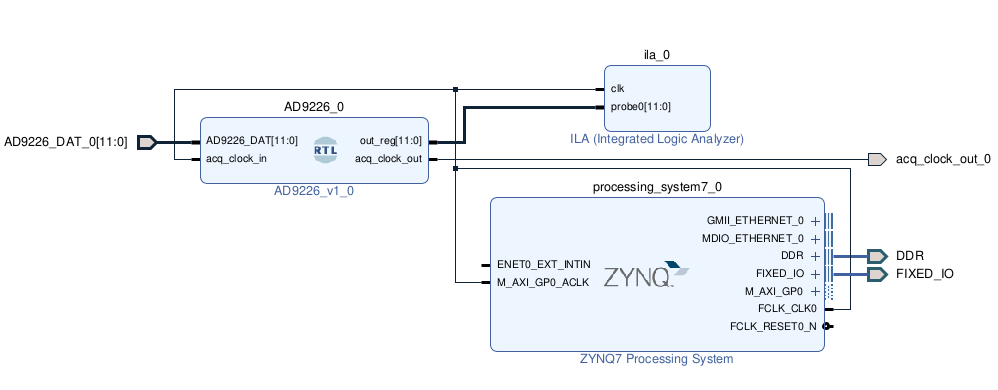

Create a block diagram. Make it look like so: I disabled all the PS system peripherals for this test.

One thing I missed was creating an HDL wrapper around the design block diagram. Right click it in sources and click "Create HDL Wrapper", and let Vivado manage it.

There was A LOT of back and forth here, but from here, I was able to start the generate bitstream and program the device. Make sure when you program the device, you ensure that the debug netlist is selected.

Things that didn't work for me: Marking nets as debug in the synthesized netlist (open sch, right click, add to debug list or something like that), the ILA core didn't get a clock. The biggest though was creating the HDL wrapper. Without that, the PL never got a clock.